Page 1 of 1

Simple Logic Analyzer for Teensy

Posted: 08 Dec 2012, 16:33

by Soarer

This side-project started while trying to figure out

oTurtlez Leading Edge DC-2014. The main purpose was simply to see what signals were output from it when, like many people, all he had was a Teensy at hand.

The Analyzer's primary use is really to assist in diagnosing problems when building my converter - you can simply load the 'portD' hex file, run hid_listen, press some keys, and copy-paste the output into the Windows app (or send it to me). Thus you can quickly see if either clock or data is dead, or if they are swapped, etc.

It can also be used more generally. The 'portB' version tracks all changes on all 8 pins of port B, while the 'portD' version tracks the state of the 8 pins of port D, but only when changes occur on PD0 to PD3. It can track changes as close together as about 1.5us, which should be enough for analyzing any keyboard related stuff. The main limit is in how the output is sent to the PC as text, so it is best suited to fairly short sequences of events (such as serial keyboard protocols!), although there is a fairly large buffer which helps.

Each sample consists of a 16-bit timestamp, the 8-bit sampled data, and a flag to indicate whether the sample was the result of a change or the timestamp wrapping past 0. Since the timebase is running at 16MHz, the resolution is 62.5ns - as long as no other interrupts get in the way! So if two transitions are more than 1.5us apart, the measured time between them will in most cases be accurate to approx +/-125ns.

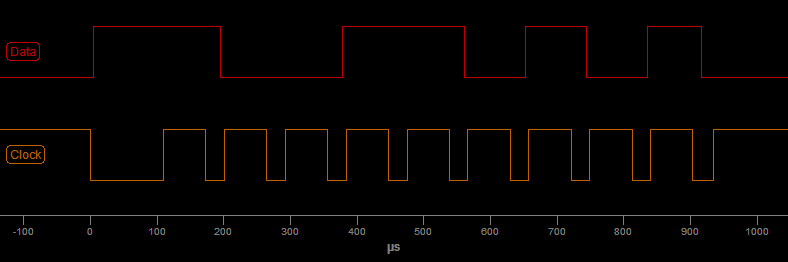

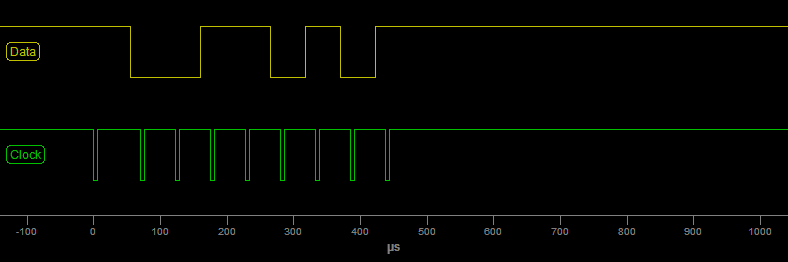

- IBM_PC_XT--Z_release.png (10.42 KiB) Viewed 27410 times

- LeadingEdge--Z_release.png (8.11 KiB) Viewed 27410 times

Notes:

- The portD version of sctrace outputs a keyboard reset signal on PB7 (for the Leading Edge).

- In scla, you can zoom in by highlighting a section of the trace with the mouse left button.

- Currently the x-axis scale is always relative to the first transition in the view.

Full source is provided. Don't laugh at the very quick and dirty nature of scla - it does the job!! The project files are for VS2003, but should easily convert to any later version. Most Windows boxes are likely to have the required DLLs (msvcr71.dll, msvcp71.dll, MFC71.dll, MFCENU71.dll) already, so I haven't included them.

Posted: 18 Jan 2014, 15:19

by Soarer

A bunch of downloads, but no replies

Has anyone tried sctrace recompiled for Teensy++ 2.0, and/or scla on Linux under Wine?

Posted: 18 Jan 2014, 15:42

by matt3o

this totally flew under my radar. thanks for your great work Soarer. I'm working on a very nice side project myself based on teensy. It's basically a switch analyzer, it presses the keys and gives a graph and a series of info regarding actuation point, weight, travel, etc... So many projects... so little time.

Posted: 18 Jan 2014, 15:50

by Soarer

Always the way

I've got a stack of 4066 chips here waiting for a project to test/analyze keyboard controllers

Posted: 19 Jan 2014, 12:16

by sethstorm

Soarer wrote:A bunch of downloads, but no replies

Has anyone tried sctrace recompiled for Teensy++ 2.0, and/or scla on Linux under Wine?

I've tried both.

What works: sctrace compiled for Teensy++ 2.0

What doesn't: scla under Wine - complains about issues with DLL's even when they are present.

Posted: 19 Jan 2014, 14:17

by kint

You guys scare me...

I don't understand a word of the first post apart from what that thing is meant to do.

That however is enough to say: wow, thanks you took the effort!

Posted: 19 Jan 2014, 14:51

by Soarer

Yeah, but... pretty colourful pictures

Right, I just tried installing Wine on Linux Mint 14 (nadia), and at first scla.exe didn't run due to missing MFC71.dll.

The solution is to run winetricks and install vcrun2003

Posted: 22 Dec 2014, 21:56

by Rotti

Sorry for the necro bump but I am attempting to use this to reverse engineer an odd ball F and I am getting output from the teensy with hid_listen but am not getting anything in scla. I am running this on a laptop with XP SP3 as my windows 8 rig lacked the requisite dll file.

Posted: 22 Dec 2014, 22:16

by Muirium

Soarer's been offline since summer, so don't hold your breath on an answer. It is an interesting project though, like so much of his stuff.

Posted: 22 Dec 2014, 23:02

by Rotti

Muirium wrote: ↑Soarer's been offline since summer, so don't hold your breath on an answer. It is an interesting project though, like so much of his stuff.

Yeah I have noticed his absence on GH as well. Its a shame with the quality of his work. I hope everything is fine on his end.

I did notice that matt30 and sethstrom might have had some luck with it and was hoping one of those two could chime in.

Posted: 25 Mar 2015, 17:40

by XMIT

FWIW, I'm planning to dust this off and test it out once my Pro Micro (ATMEGAu32) boards arrive.

Come back Soarer!

Posted: 01 Nov 2015, 10:54

by gogusrl

Did you ever got around that XMIT ? I've got a space invaders that needs figuring out and only got pro micro's available.

Posted: 01 Nov 2015, 11:34

by XMIT

Nothing yet, sorry. I ended up buying some Saleae clones for my logic analyzer needs.

Posted: 22 Feb 2016, 23:40

by inyourgroove

Was anyone able to get this to work I am in the same state as Rotti. I can see data on hid_listen but no data in scla. If only I understood what hid_listen was printing I could just use that data and forget about scla. Looking at the scla source code that is posted, it does not seem to do anything. There isn't any interesting code that would be interpreting the data from usb and displaying the graphs.

Posted: 23 Feb 2016, 02:26

by inyourgroove

So I need to read more carefully. The OP says to copy paste the output of hid_listen into scla. Once you know to do that it works great.

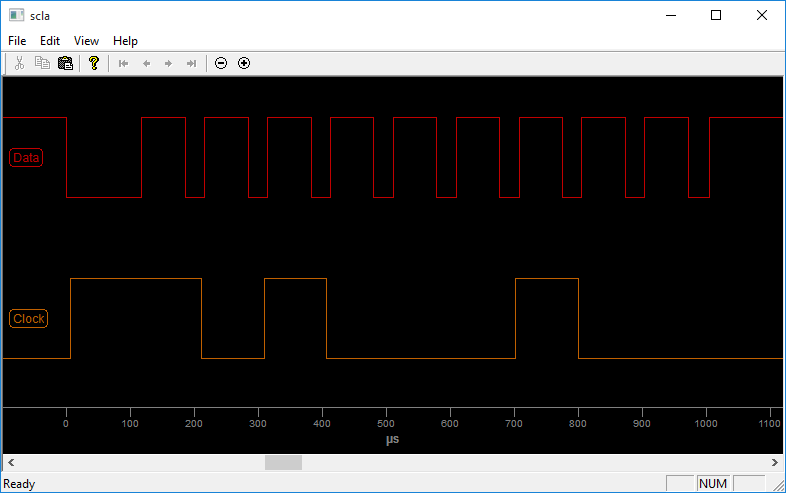

- scla.png (9.64 KiB) Viewed 24572 times

Seems I have my clock and data lines reversed.

Re: Simple Logic Analyzer for Teensy

Posted: 01 Jan 2022, 14:12

by hasu

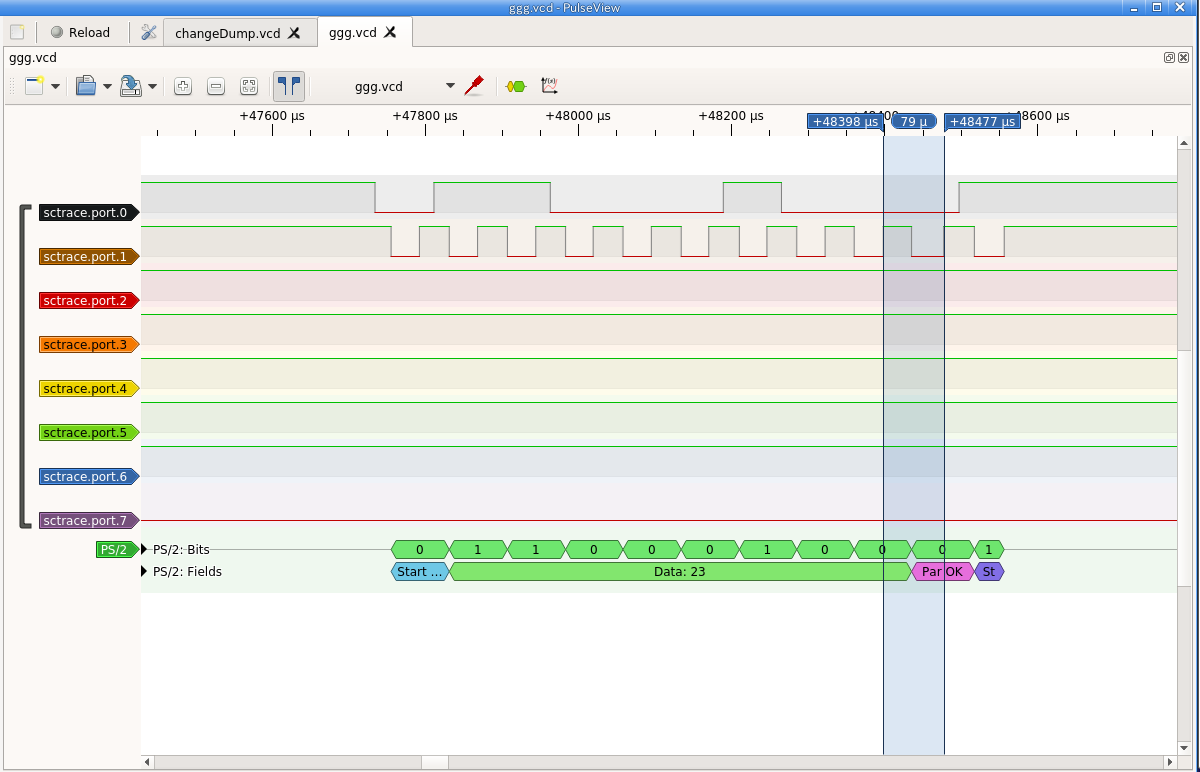

Came here to this simple script that converts Soarer's output format into VCD(value change dump). VCD file can be read by PulseView.

-

https://sigrok.org/wiki/PulseView

-

https://en.wikipedia.org/wiki/Value_change_dump

-

https://sigrok.org/wiki/File_format:Vcd

- Screenshot_2022-01-01_21-59-13.png (58.73 KiB) Viewed 18187 times

Code: Select all

#!/usr/bin/python3

# -*- Mode: Python; coding: utf-8; indent-tabs-mode: nil; tab-width: 4 -*-

#

# Converts Soarer's Logic Analyzer output into VCD format

# https://deskthority.net/viewtopic.php?t=4567

#

# 'sctrace' record is comprised of seven hex characters(0-9A-F):

# time: 4 chars/2 bytes; timestamp of event

# stat: 2 chars/1 byte; port state

# flag: 1 char /4 bits; timer event(1) or port state change event(0)

import sys

# https://github.com/westerndigitalcorporation/pyvcd

from vcd import VCDWriter

if len(sys.argv) < 2:

print(f"Usage: {sys.argv[0]} infile")

sys.exit(1)

# read 'sctrace' output file

with open(sys.argv[1], "r") as file:

for line in file:

for record in line.strip().split():

if len(record) == 7:

time = int(record[0:4], 16)

port = int(record[4:6], 16)

flag = int(record[6:7], 16)

#print(time, port, flag)

# write VCD

from datetime import datetime

with VCDWriter(sys.stdout, timescale='1 us', date=datetime.utcnow().ctime()) as writer:

# prams: scope, name, var_type, size

port = writer.register_var('sctrace', 'port', 'wire', size=8)

# read 'sctrace' output file

with open(sys.argv[1], "r") as file:

ext_time = 0

for line in file:

for record in line.strip().split():

if len(record) == 7:

time = int(record[0:4], 16)

stat = int(record[4:6], 16)

flag = int(record[6:7], 16)

# timer overflow when flag == 1

if flag:

ext_time += 1

# time: 1/16 us(62.5 ns) per tick(@16MHz+Prescaler:0)

writer.change(port, ((ext_time * 0x10000) + time)/16, stat)

Re: Simple Logic Analyzer for Teensy

Posted: 01 Jan 2022, 14:53

by Muirium

Now

that is how to necro!